# SIMetrix/SIMPUS

# SIMPLIS REFERENCE MANUAL

VERSION 9.0

NOVEMBER 2021

# SIMPLIS REFERENCE MANUAL

COPYRIGHT © SIMPLIS TECHNOLOGIES INC. 1992-2021

SIMPLIS Technologies, Inc. P.O. Box 40084 Portland, OR 97240-0084 USA

Tel: +1 503 766 3928 Fax: +1 503 296 5674

Email: info@simplistechnologies.com Web: http://simplistechnologies.com

# **Contents**

| 1 | Intro                     | oduction                                    | 1      |  |  |

|---|---------------------------|---------------------------------------------|--------|--|--|

|   | 1.1                       | Overview                                    | 1      |  |  |

|   | 1.2                       | Organization of this User Manual            | 1      |  |  |

| 2 | 2 Input File Organization |                                             |        |  |  |

|   | 2.1                       | Overview                                    | 3      |  |  |

|   | 2.2                       |                                             | 3      |  |  |

|   |                           |                                             | 3      |  |  |

|   |                           | Blank Characters                            | 3      |  |  |

|   |                           | Blank Lines                                 | 3      |  |  |

|   |                           |                                             | 4      |  |  |

|   |                           |                                             | 4      |  |  |

|   |                           |                                             | 4      |  |  |

|   |                           |                                             | 4      |  |  |

|   |                           |                                             | 5      |  |  |

|   |                           |                                             | 5      |  |  |

|   |                           |                                             | 6      |  |  |

|   |                           |                                             | 6      |  |  |

|   |                           |                                             | 8      |  |  |

|   |                           |                                             | 9      |  |  |

|   | 2.3                       | · ·                                         | ر<br>9 |  |  |

|   | 2.5                       |                                             | 9      |  |  |

|   |                           | Main Circuit                                |        |  |  |

|   |                           | Subcircuit                                  |        |  |  |

|   |                           |                                             |        |  |  |

|   |                           | General Statements                          | 1      |  |  |

| 3 | Devi                      | ce Statements 12                            | 2      |  |  |

|   | 3.1                       | Overview                                    | 2      |  |  |

|   |                           | Device Statement Format                     | 2      |  |  |

|   |                           | Node Names                                  | 2      |  |  |

|   |                           | Voltage and Current Polarity Conventions    | 3      |  |  |

|   |                           | Parameter Assignments                       | 3      |  |  |

|   |                           | Controlling Devices                         | 4      |  |  |

|   | 3.2                       | SIMPLIS Device Types                        | 4      |  |  |

|   |                           | Linear Resistors                            | 4      |  |  |

|   |                           | Linear Inductors and Capacitors             | 4      |  |  |

|   |                           | Independent Voltage and Current Sources     |        |  |  |

|   |                           | Triangular Sources                          |        |  |  |

|   |                           | Square Wave Sources                         |        |  |  |

|   |                           | Pulse Sources with Zero Rise and Fall Times |        |  |  |

|   |                           | Sinusoidal Sources                          |        |  |  |

|   |                           | Cosinusoidal Source                         |        |  |  |

|   |                           | Aperiodic Exponential Pulse Sources         |        |  |  |

|   |                           | Aperiodic Piecewise-Linear Sources          |        |  |  |

|   |            | Mutual Inductances30Linear Voltage-Controlled Sources32Linear Current-Controlled Sources32Ideal Transformers34Simple Switches34Simple Transistor Switches35Piecewise Linear Resistors36Piecewise-Linear Inductors and Capacitors37Simple Logic Gates37Subcircuit Calls / Instantiation38 |

|---|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | Mod        | el Statements 40                                                                                                                                                                                                                                                                         |

|   | 4.1        | Overview                                                                                                                                                                                                                                                                                 |

|   | 4.2        | Device Models Used in Simplis                                                                                                                                                                                                                                                            |

|   |            | Piecewise-Linear Resistor Models                                                                                                                                                                                                                                                         |

|   |            | Piecewise-Linear Inductor and Capacitor Models                                                                                                                                                                                                                                           |

|   |            | Simple Switch Models                                                                                                                                                                                                                                                                     |

|   |            | Simple Transistor Switch Models                                                                                                                                                                                                                                                          |

|   |            | Simple Logic Device Models                                                                                                                                                                                                                                                               |

| 5 | Subo       | circuit Definition 70                                                                                                                                                                                                                                                                    |

|   | 5.1        | Overview                                                                                                                                                                                                                                                                                 |

|   | 5.2        | Subcircuit Definition                                                                                                                                                                                                                                                                    |

|   |            | Parent and Child Relationships for Subcircuits                                                                                                                                                                                                                                           |

|   |            | .SUBCKT Statement                                                                                                                                                                                                                                                                        |

|   |            | .ENDS Statement (End of Subcircuit Statement)                                                                                                                                                                                                                                            |

|   | 5.3        | Scope of Definition                                                                                                                                                                                                                                                                      |

|   |            | The Scope of Definition for the Main Circuit                                                                                                                                                                                                                                             |

|   | 5.4        | Scope of Definition for a Device and for a Node                                                                                                                                                                                                                                          |

|   | 5.5        | External and Local Nodes                                                                                                                                                                                                                                                                 |

|   | 5.6        | Subcircuit Calls/Instantiation                                                                                                                                                                                                                                                           |

|   |            |                                                                                                                                                                                                                                                                                          |

| 6 |            | trol Statements 77                                                                                                                                                                                                                                                                       |

|   | 6.1        | Overview                                                                                                                                                                                                                                                                                 |

|   | 6.2<br>6.3 | Option Statements                                                                                                                                                                                                                                                                        |

|   | 0.5        | Linear and PWL Capacitors                                                                                                                                                                                                                                                                |

|   |            | Linear and PWL Inductors                                                                                                                                                                                                                                                                 |

|   |            | Setting of Initial States for S and Q Switches                                                                                                                                                                                                                                           |

|   |            | Setting of Initial Segment for PWL Resistors                                                                                                                                                                                                                                             |

|   |            | Setting of Initial State for Simple Logic Gates                                                                                                                                                                                                                                          |

|   |            | Initial Conditions for Devices in a Subcircuit                                                                                                                                                                                                                                           |

|   | 6.4        | Control Statements for Printing Variables                                                                                                                                                                                                                                                |

|   |            | PRINT                                                                                                                                                                                                                                                                                    |

|   | 6.5        | KEEP                                                                                                                                                                                                                                                                                     |

|   | 6.5<br>6.6 | Mapping Names to Node Numbers                                                                                                                                                                                                                                                            |

|   | 6.7        | Statements Associated with Analyses                                                                                                                                                                                                                                                      |

|   | 0.7        | TRAN - Time-Domain Transient Analysis                                                                                                                                                                                                                                                    |

|   |            | .POP - Periodic Operating Point Analysis                                                                                                                                                                                                                                                 |

|   |            | .AC - Frequency Domain Analysis                                                                                                                                                                                                                                                          |

|   | _          |                                                                                                                                                                                                                                                                                          |

| 7 |            | ning SIMPLIS                                                                                                                                                                                                                                                                             |

|   | 7.1        | Overview                                                                                                                                                                                                                                                                                 |

|   | 7.2        | Running SIMPLIS on a SIMetrix Schematic                                                                                                                                                                                                                                                  |

|   |            | rading Land retion Lines                                                                                                                                                                                                                                                                 |

|    | 7.3                                                                                         | Running SIMPLIS for an External Netlist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91                                                                                                                         |

|----|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|    | 7.4                                                                                         | Running SIMPLIS from a Script                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 91                                                                                                                         |

|    | 7.5                                                                                         | Running SIMPLIS from a DOS Prompt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

|    | 7.6                                                                                         | SIMPLIS Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 92                                                                                                                         |

|    | 7.7                                                                                         | Aborting a SIMPLIS Run                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92                                                                                                                         |

|    | 7.8                                                                                         | Automatic Program Suspension by SIMPLIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 93                                                                                                                         |

|    | 7.9                                                                                         | Netlist Preprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 93                                                                                                                         |

|    | 1.5                                                                                         | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93                                                                                                                         |

|    |                                                                                             | Launching Preprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 94                                                                                                                         |

|    |                                                                                             | Library Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 94                                                                                                                         |

|    |                                                                                             | Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 95                                                                                                                         |

|    |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 95                                                                                                                         |

|    |                                                                                             | Passing Parameters to Subcircuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

|    |                                                                                             | Conditional Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95                                                                                                                         |

|    | <b>-</b> 10                                                                                 | Looping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96                                                                                                                         |

|    | 7.10                                                                                        | Running Monte Carlo and Multi-step Analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 96                                                                                                                         |

| 8  | Cima                                                                                        | plis Data Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97                                                                                                                         |

| 0  | 8.1                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97<br>97                                                                                                                   |

|    |                                                                                             | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

|    | 8.2                                                                                         | The Listing Data File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97                                                                                                                         |

|    | 8.3                                                                                         | Error Message Data File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 97                                                                                                                         |

|    | 8.4                                                                                         | The "State of Exit" Data File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 98                                                                                                                         |

|    | 8.5                                                                                         | Switching Instance Data File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 98                                                                                                                         |

|    | 8.6                                                                                         | Time-domain Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98                                                                                                                         |

|    | 8.7                                                                                         | The Topology Information File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                            |

|    | 8.8                                                                                         | Taking Advantage of Existing Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 99                                                                                                                         |

|    | 8.9                                                                                         | Switching Instance Data for POP Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                                                                                                                        |

|    | 8.10                                                                                        | Data for the Periodic Operating Point Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100                                                                                                                        |

|    | 8.11                                                                                        | Print/Plot File for Frequency-Domain Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100                                                                                                                        |

|    |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| n  | G!                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 101                                                                                                                        |

| 9  | -                                                                                           | plis-TX Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 101                                                                                                                        |

| 9  | 9.1                                                                                         | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101                                                                                                                        |

| 9  | 9.1<br>9.2                                                                                  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101<br>101                                                                                                                 |

| 9  | 9.1<br>9.2<br>9.3                                                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101<br>101<br>103                                                                                                          |

| 9  | 9.1<br>9.2<br>9.3<br>9.4                                                                    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101<br>101<br>103<br>105                                                                                                   |

| 9  | 9.1<br>9.2<br>9.3<br>9.4<br>9.5                                                             | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101<br>103<br>103<br>105                                                                                                   |

| 9  | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6                                                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101<br>103<br>103<br>105<br>107                                                                                            |

| 9  | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7                                               | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101<br>103<br>103<br>105<br>107<br>109                                                                                     |

| 9  | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6                                                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 101<br>103<br>103<br>105<br>107<br>109                                                                                     |

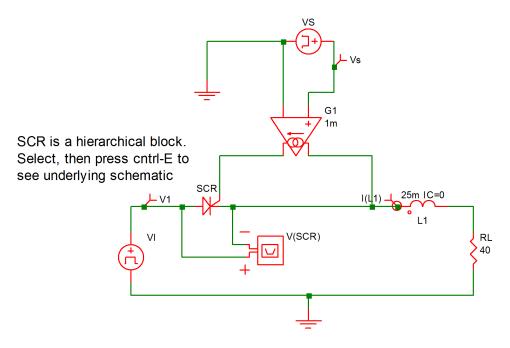

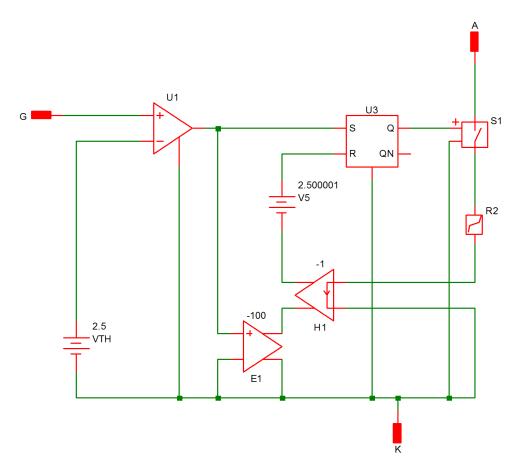

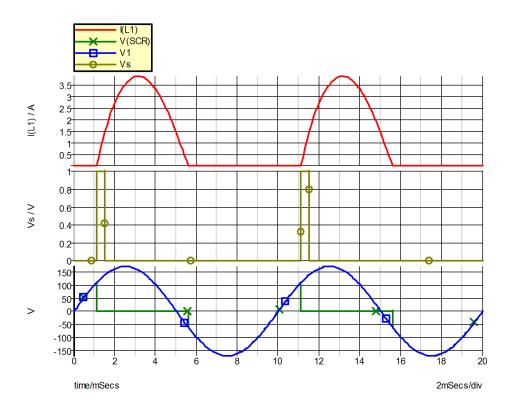

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8                                        | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load                                                                                                                                                                                                                                                                                                                                                                                                                                    | 101<br>103<br>105<br>107<br>109<br>112                                                                                     |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8                                        | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP                                                                                                                                                                                                                                                                                                                                                                                                                          | 101<br>103<br>105<br>107<br>109<br>112<br>114                                                                              |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b>                         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP  Overview                                                                                                                                                                                                                                                                                                                                                                                                                | 101<br>103<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b>                                                         |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b>                         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP  Overview  Statements Relating to POP Analysis                                                                                                                                                                                                                                                                                                                                                                           | 101<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b><br>118                                                         |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b>                         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis                                                                                                                                                                                                                                                                                                                                          | 101<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b><br>119                                                         |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis                                                                                                                                                                                                                                                                                                    | 101<br>103<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b><br>119<br>119                                           |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis                                                                                                                                                                                                                                                 | 101<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b><br>119                                                         |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP  Overview  Statements Relating to POP Analysis  POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis                                                                                                                                                                                                           | 101<br>103<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b><br>119<br>119                                           |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis                                                                                                                                                                                                                                                 | 101<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b><br>119<br>119<br>123                                           |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load   plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis  How POP Deals with Time Varying Sources                                                                                                                                                                | 101<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b><br>118<br>119<br>123<br>125<br>127                             |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load  plis-POP  Overview  Statements Relating to POP Analysis  POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis                                                                                                                                                                                                           | 101<br>103<br>105<br>107<br>109<br>112<br>114<br><b>118</b><br>118<br>119<br>123<br>125<br>127<br>127                      |

| 10 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load   plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis  How POP Deals with Time Varying Sources  The POP_SHOWDATA option for POP Analysis  Example of Applying the POP Analysis Tool                                                                           | 101<br>103<br>105<br>107<br>109<br>112<br>114<br>118<br>119<br>123<br>125<br>127<br>130<br>131                             |

| 10 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2         | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load   plis-POP  Overview  Statements Relating to POP Analysis  POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis  How POP Deals with Time Varying Sources  The POP_SHOWDATA option for POP Analysis  Example of Applying the POP Analysis Tool                                                                            | 101<br>103<br>105<br>107<br>109<br>112<br>114<br>118<br>119<br>123<br>125<br>127<br>130<br>131                             |

| 10 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2<br>10.3 | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load   plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis  How POP Deals with Time Varying Sources  The POP_SHOWDATA option for POP Analysis  Example of Applying the POP Analysis Tool  plis-FX  Overview                                                        | 101<br>103<br>105<br>107<br>109<br>112<br>114<br>118<br>119<br>123<br>125<br>127<br>130<br>131                             |

| 10 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2<br>10.3 | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load   plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis  How POP Deals with Time Varying Sources  The POP_SHOWDATA option for POP Analysis  Example of Applying the POP Analysis Tool  plis-FX  Overview  Statements Relating AC Analysis                       | 101<br>103<br>105<br>107<br>109<br>112<br>114<br>118<br>119<br>123<br>125<br>127<br>130<br>131                             |

| 10 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2<br>10.3 | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load   plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis  The Time Variable During POP Analysis  The POP_SHOWDATA option for POP Analysis  Example of Applying the POP Analysis Tool  plis-FX  Overview  Statements Relating AC Analysis  .AC Analysis Statement | 101<br>103<br>105<br>107<br>109<br>112<br>114<br>118<br>119<br>123<br>125<br>127<br>130<br>131                             |

| 10 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2<br>10.3 | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load   plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis  How POP Deals with Time Varying Sources  The POP_SHOWDATA option for POP Analysis  Example of Applying the POP Analysis Tool  plis-FX  Overview  Statements Relating AC Analysis                       | 101<br>103<br>105<br>107<br>109<br>112<br>114<br>118<br>119<br>123<br>125<br>127<br>130<br>131<br>135<br>135               |

| 10 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br><b>Simp</b><br>10.1<br>10.2<br>10.3 | Overview  Example: Rectifier with RC load  Example: 3-Phase Rectifier with Resistive Load  Example: Op-amp with Saturation  Example: Unregulated Converter  Example: Regulated Converter  Example: Saturable Inductor  Example: SCR with RL Load   plis-POP  Overview  Statements Relating to POP Analysis  .POP Statement for POP Analysis  Options Associated with POP Analysis  Synopsis of the Periodic Operating Point Analysis  The Time Variable During POP Analysis  The Time Variable During POP Analysis  The POP_SHOWDATA option for POP Analysis  Example of Applying the POP Analysis Tool  plis-FX  Overview  Statements Relating AC Analysis  .AC Analysis Statement | 101<br>103<br>105<br>107<br>109<br>112<br>114<br>118<br>119<br>123<br>125<br>127<br>127<br>130<br>131<br>135<br>137<br>137 |

|    |      | Amplitude of Small-Signal AC Sources                                     | 0  |

|----|------|--------------------------------------------------------------------------|----|

|    |      | Phase Delay of Small-Signal AC Sources                                   | .1 |

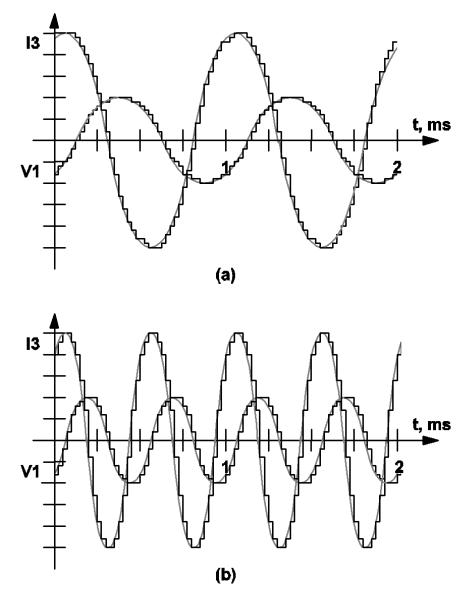

|    |      | Sample Waveforms of AC Sources Continuous Domain                         | .1 |

|    |      | Sample Waveforms of AC Sources Discrete Domain                           | .2 |

|    |      | Continuous and Discrete Domain Differences                               | .3 |

|    |      | AC Analysis Behaviour of Time-Varying Sources                            | 4  |

|    |      | Behaviour of AC Sources in Transient and POP                             | .5 |

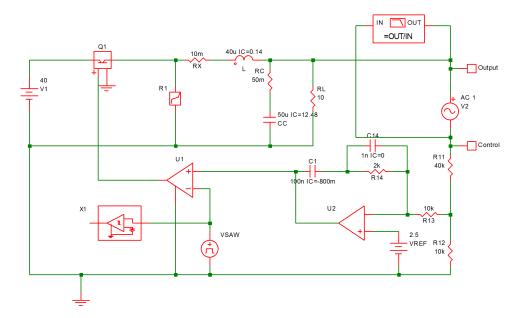

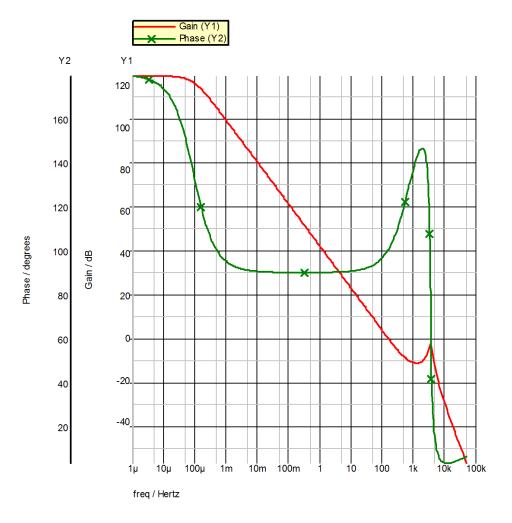

|    |      | Example of Applying the AC Analysis Tool                                 | .5 |

|    |      |                                                                          |    |

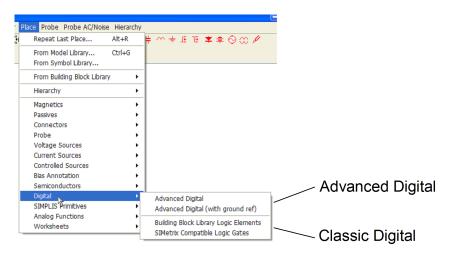

| 12 |      | anced Digital Components 14                                              |    |

|    | 12.1 | Overview                                                                 | _  |

|    |      | Major Benefits                                                           | _  |

|    |      | New Digital Features                                                     |    |

|    |      | Advanced Digital Components                                              | -  |

|    |      | Classic Components                                                       |    |

|    |      | Similarities Between Classic and Advanced Digital Components             |    |

|    |      | Differences between Classic and Advanced Digital Components              |    |

|    |      | Strategies for Deploying the new Advanced Digital Components             |    |

|    |      | A Simple DEMO Circuit                                                    |    |

|    | 12.2 | Advanced Component Reference                                             |    |

|    |      | Introduction                                                             |    |

|    |      | General Behaviour                                                        |    |

|    |      | Parts Available Summary                                                  |    |

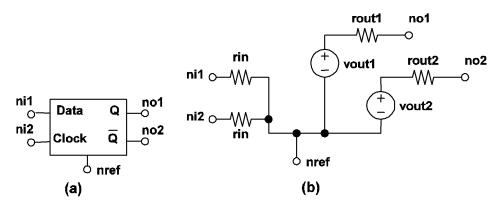

|    |      | D-Type Flip-Flop                                                         |    |

|    |      | D-Type Flip-Flop w/ SET/RST                                              |    |

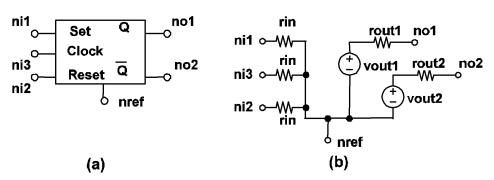

|    |      | S/R Flip-Flop                                                            |    |

|    |      | S/R Flip-Flop w/ SET/RST                                                 |    |

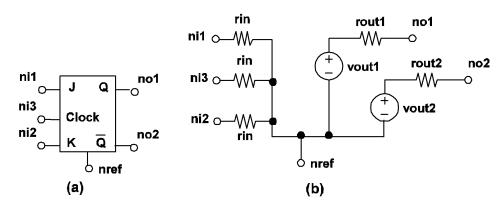

|    |      | J/K Flip-Flop                                                            |    |

|    |      | J/K Flip-Flop w/ SET/RST                                                 |    |

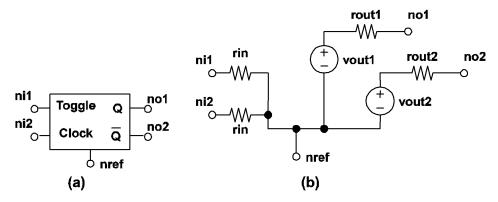

|    |      | Toggle Flip-Flop                                                         | 3  |

|    |      | Toggle Flip-Flop w/ SET/RST                                              | 6  |

|    |      | AND Gate                                                                 |    |

|    |      | NAND Gate                                                                | 0  |

|    |      | OR Gate                                                                  | 1  |

|    |      | NOR Gate                                                                 | 2  |

|    |      | Exclusive-OR Gate                                                        |    |

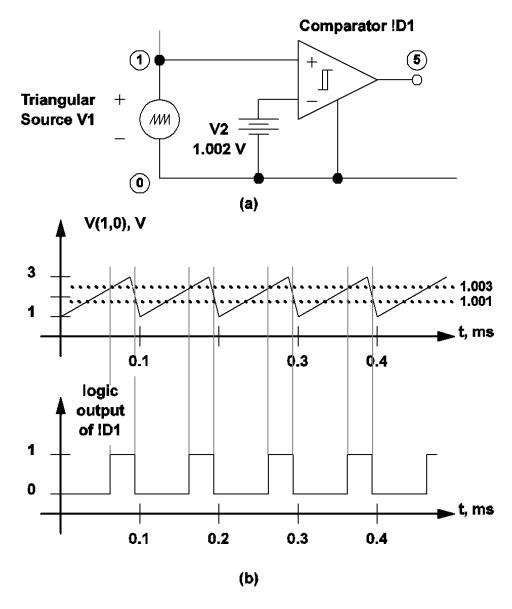

|    |      | Comparator                                                               |    |

|    |      | Buffer                                                                   | 6  |

|    |      | Inverter                                                                 | 7  |

|    |      | Adder                                                                    | 9  |

|    |      | Subtracter                                                               | 1  |

|    |      | Multiplier                                                               | 3  |

|    |      | Divider                                                                  | 5  |

|    |      | Fixed Point Divider                                                      | 7  |

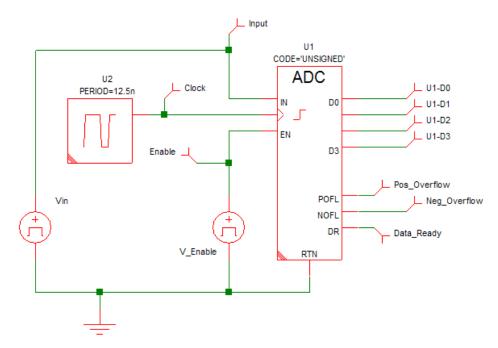

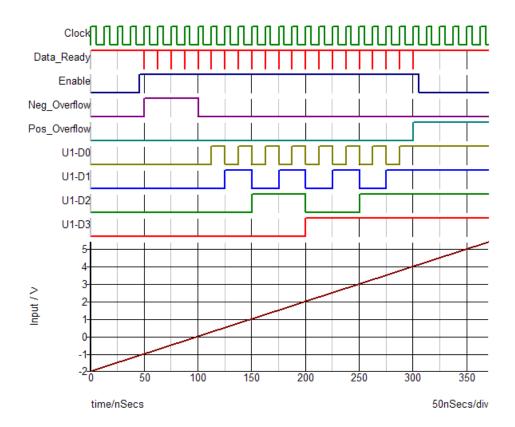

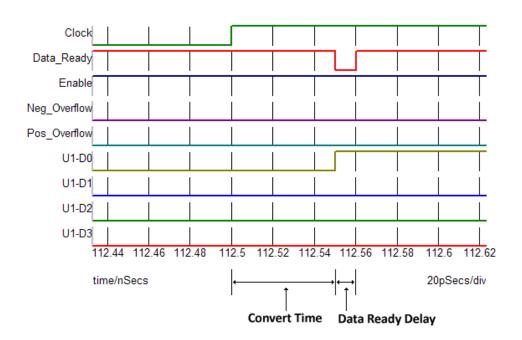

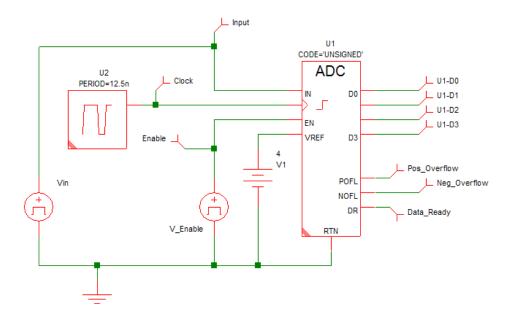

|    |      | Analog to Digital Converter - Operation                                  | 0  |

|    |      | Analog to Digital Converter - Parameters                                 | 2  |

|    |      | Analog to Digital Converter w/ Adjustable Voltage Reference - Operation  | 5  |

|    |      | Analog to Digital Converter w/ Adjustable Voltage Reference - Parameters | 15 |

|    |      | Digital to Analog Converter (Non-clocked)                                | 8  |

|    |      | Digital Pulse Source                                                     | 0  |

|    |      | Digital Signal Source                                                    | 1  |

|    |      | Asymmetric Delay                                                         | 3  |

|    |      | Digital Comparator                                                       | 4  |

|    |      | Digital Constant                                                         | 6  |

|    |      | Digital Lookup Table                                                     |    |

|    |      | Digital Lookup Table allowing Don't Care in Input Definition 21          | 8  |

# Contents

| Digital Mux                         |  |  | 219 |

|-------------------------------------|--|--|-----|

| Digital Demux                       |  |  | 221 |

| Up Counter                          |  |  |     |

| Down Counter                        |  |  | 226 |

| Up/Down Counter                     |  |  | 229 |

| D-Type Latch                        |  |  |     |

| S/R Latch                           |  |  | 234 |

| S/R Latch w/ Enable                 |  |  | 236 |

| Data Register                       |  |  | 238 |

| Shift Register                      |  |  | 242 |

| Shift Register (Left)               |  |  | 246 |

| Shift Register (Right)              |  |  | 249 |

| Shift Register (Multi-bit)          |  |  | 253 |

| Barrel Shifter                      |  |  | 256 |

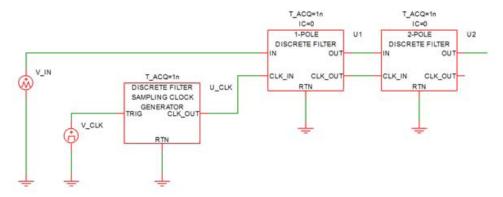

| 1-Pole Discrete Filter - Operation  |  |  | 260 |

| 1-Pole Discrete Filter - Parameters |  |  | 261 |

| 2-Pole Discrete Filter - Operation  |  |  | 261 |

| 2-Pole Discrete Filter - Parameters |  |  | 262 |

| PID Discrete Filter - Operation     |  |  | 263 |

| PID Discrete Filter - Parameters    |  |  | 265 |

# **Chapter 1**

# Introduction

### 1.1 Overview

This manual provides detailed reference material for the SIMPLIS (SIMulation for Piecewise-Linear System) simulation package. It is intended for those who want to develop a more in-depth understanding of this software package.

SIMPLIS is a computer software package specifically designed for the simulation and analysis of switching power supplies. In a typical switching power system, the transistors and the diodes function as switches, allowing the system to be characterized by a cyclical sequence of linear circuit topologies. By taking advantage of the repetitive piecewise-linear structure of such systems, SIMPLIS is able to perform the simulation in an efficient and accurate manner.

In order to avoid potential problems caused by simple syntax errors, SIMPLIS automatically checks the syntax of the input file provided by the user. If syntax errors are detected in the input file, error messages are recorded in a file for the user to inspect and correct the errors. This feature allows the user to detect and correct errors quickly and efficiently.

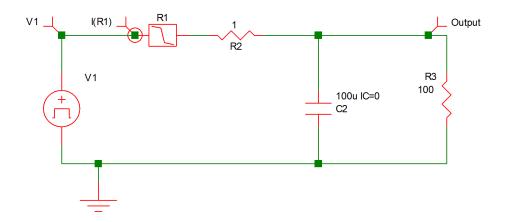

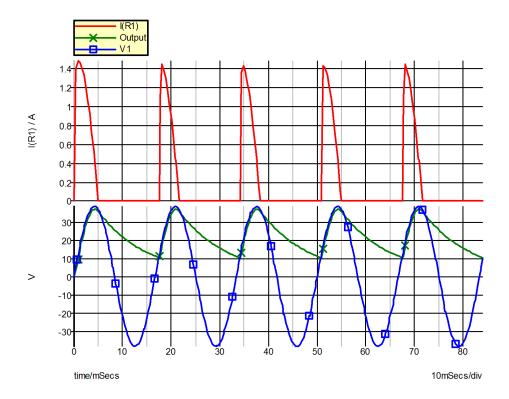

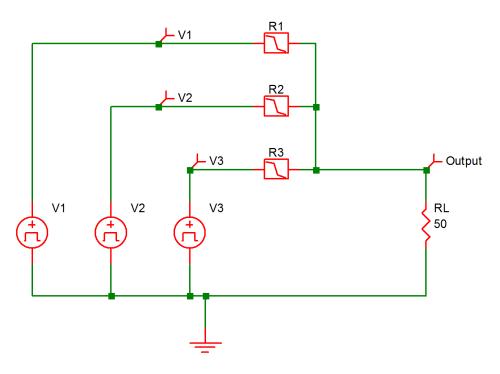

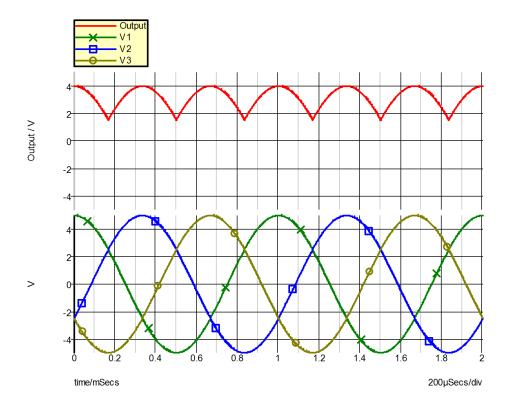

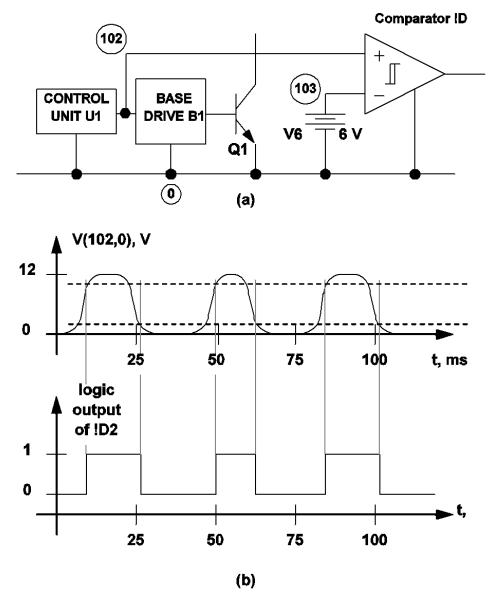

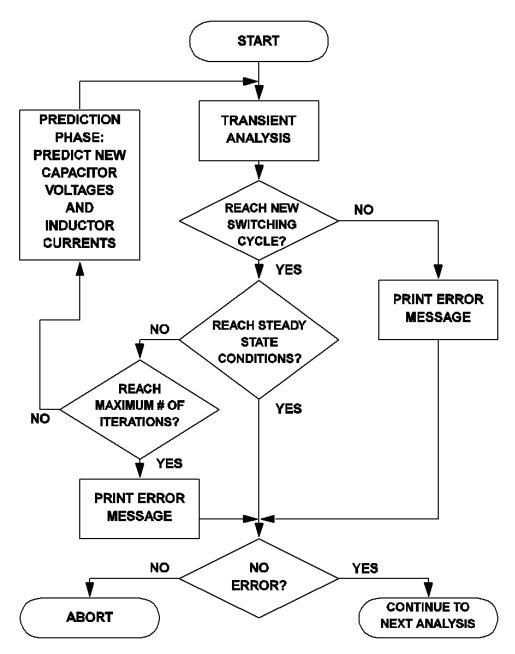

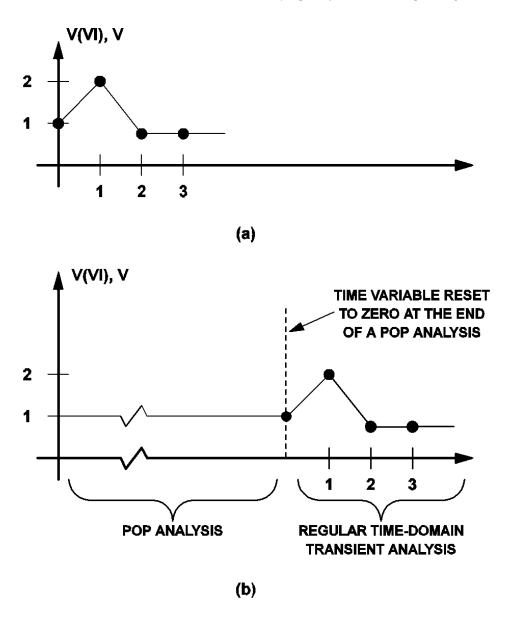

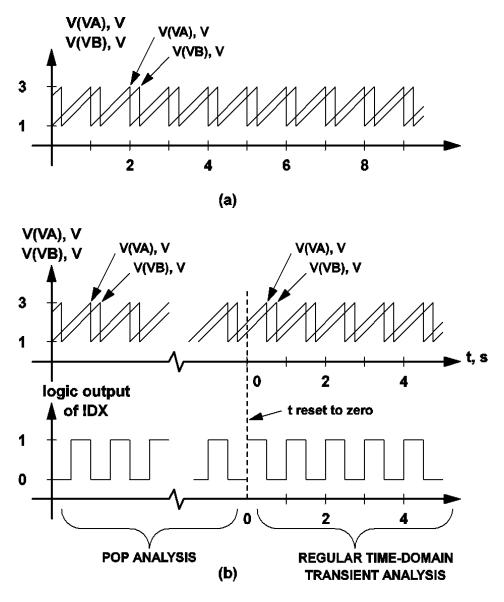

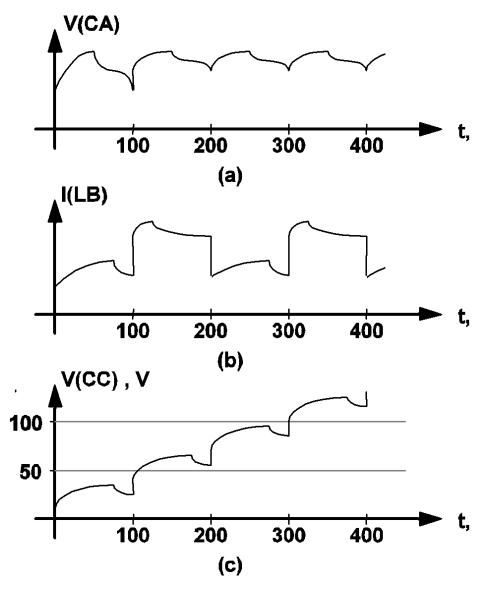

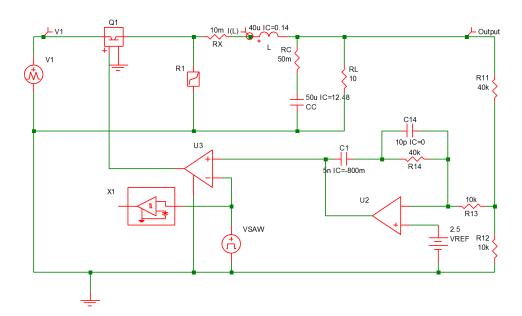

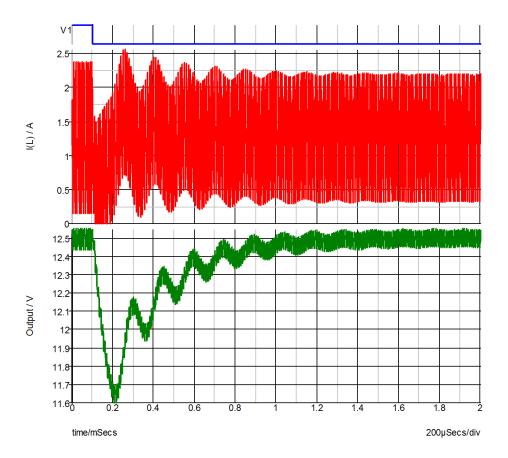

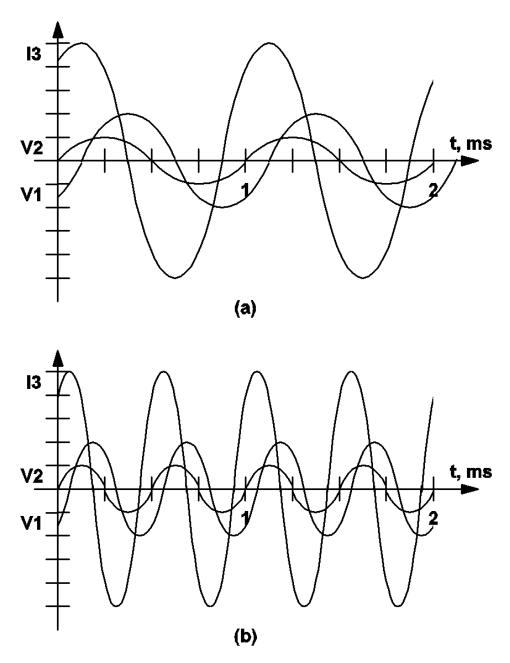

SIMPLIS-TX is a two-pass time-domain simulator. In the first pass of a simulation run, only the data pertaining to the state of the simulation at the switching instances are saved. In the second pass, called the Post-Simulation Processing run, detailed waveform information is reconstructed from the data generated in the first pass. At the user-interface level, these two separate operations are not distinguishable since they are executed automatically by SIMPLIS. Thus SIMPLIS appears as a one-pass simulator to the user. This internal two-step simulation technique optimizes the simulation speed and versatility of SIMPLIS.